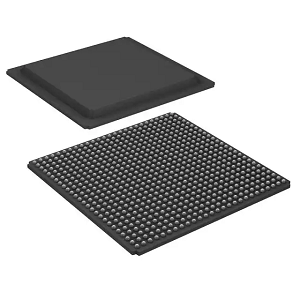

XC7Z030-2FFG676I – Circuits intégrés (CI), embarqués, système sur puce (SoC)

Attributs du produit

| TAPER | DESCRIPTION |

| Catégorie | Circuits intégrés (CI) |

| Fabricant | DMLA |

| Série | Zynq®-7000 |

| Emballer | Plateau |

| État du produit | Actif |

| Architecture | MCU, FPGA |

| Processeur principal | Double ARM® Cortex®-A9 MPCore™ avec CoreSight™ |

| Taille du flash | - |

| Taille de la RAM | 256 Ko |

| Périphériques | DMLA |

| Connectivité | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Vitesse | 800 MHz |

| Attributs principaux | Kintex™-7 FPGA, 125 000 cellules logiques |

| Température de fonctionnement | -40 °C ~ 100 °C (TJ) |

| Colis/Caisse | 676-BBGA, FCBGA |

| Package d'appareil du fournisseur | 676-FCBGA (27x27) |

| Nombre d'E/S | 130 |

| Numéro de produit de base | XC7Z030 |

Documents et médias

| TYPE DE RESSOURCE | LIEN |

| Feuilles de données | Présentation du SoC entièrement programmable Zynq-7000 |

| Modules de formation sur les produits | Alimenter les FPGA Xilinx série 7 avec les solutions de gestion de l'alimentation TI |

| Informations environnementales | Certifié RoHS de Xiliinx |

| Produit en vedette | Tous les SoC Zynq®-7000 programmables |

| Conception/Spécification PCN | Matériel de développement multiple Chg 16/déc/2019 |

| Errata | Errata Zynq-7000 |

Classifications environnementales et d'exportation

| ATTRIBUT | DESCRIPTION |

| Statut RoHS | Conforme ROHS3 |

| Niveau de sensibilité à l'humidité (MSL) | 4 (72 heures) |

| Statut REACH | REACH non affecté |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Unité de processeur d'application (APU)

Les principales caractéristiques de l'APU comprennent :

• MPCores ARM Cortex-A9 double cœur ou monocœur.Les fonctionnalités associées à chaque noyau incluent :

• 2,5 DMIPS/MHz

• Plage de fréquence de fonctionnement :

- Z-7007S/Z-7012S/Z-7014S (liaison filaire) : jusqu'à 667 MHz (-1) ;766 MHz (-2)

- Z-7010/Z-7015/Z-7020 (liaison filaire) : jusqu'à 667 MHz (-1) ;766 MHz (-2) ;866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (puce retournée) : 667 MHz (-1) ;800 MHz (-2) ;1 GHz (-3)

- Z-7100 (puce retournée) : 667 MHz (-1) ;800 MHz (-2)

• Possibilité de fonctionner en modes monoprocesseur, double processeur symétrique et double processeur asymétrique

• Virgule flottante simple et double précision : jusqu'à 2,0 MFLOPS/MHz chacune

• Moteur de traitement multimédia NEON pour la prise en charge SIMD

• Prise en charge de Thumb®-2 pour la compression du code

• Caches de niveau 1 (instructions et données séparées, 32 Ko chacune)

- Ensemble 4 voies associatif

- Cache de données non bloquant avec prise en charge jusqu'à quatre échecs de lecture et d'écriture en suspens chacun

• Unité de gestion de mémoire intégrée (MMU)

• TrustZone® pour un fonctionnement en mode sécurisé

• Interface de port de cohérence d'accélérateur (ACP) permettant des accès cohérents du PL à l'espace mémoire du CPU

• Cache unifié de niveau 2 (512 Ko)

• Ensemble associatif à 8 voies

• TrustZone activé pour un fonctionnement sécurisé

• RAM sur puce à double port (256 Ko)

• Accessible par CPU et logique programmable (PL)

• Conçu pour un accès à faible latence depuis le processeur

• DMA à 8 canaux

• Prend en charge plusieurs types de transfert : mémoire à mémoire, mémoire à périphérique, périphérique à mémoire et dispersion-collecte.

• Interface AXI 64 bits, permettant des transferts DMA à haut débit

• 4 chaînes dédiées au PL

• TrustZone activé pour un fonctionnement sécurisé

• Les interfaces d'accès à double registre imposent la séparation entre les accès sécurisés et non sécurisés.

• Interruptions et minuteries

• Contrôleur d'interruption générale (GIC)

• Trois minuteries de chien de garde (WDT) (une par CPU et une WDT système)

• Deux minuteries/compteurs triples (TTC)

• Prise en charge du débogage et du suivi CoreSight pour Cortex-A9

• Macrocellule de trace de programme (PTM) pour l'instruction et la trace

• Interface de déclenchement croisé (CTI) permettant des points d'arrêt et des déclencheurs matériels