DS90UB953TRHBRQ1 (composants électroniques puces IC circuits intégrés IC) DS90UB953TRHBRQ1

Attributs du produit

| TAPER | DESCRIPTION | SÉLECTIONNER |

| Catégorie | Circuits intégrés (CI)Interface Sérialiseurs, désérialiseurs |

|

| Fabricant | Texas Instruments |

|

| Série | Automobile, AEC-Q100 |

|

| Emballer | Bande et bobine (TR)Bande coupée (CT) Digi-Reel® |

|

| État du produit | Actif |

|

| Fonction | Sérialiseur |

|

| Débit de données | 4,16 Gbit/s |

|

| Type d'entrée | CSI-2, MIPI |

|

| Le type de sortie | FPD-Link III, LVDS |

|

| Nombre d'entrées | 1 |

|

| Nombre de sorties | 1 |

|

| Tension - Alimentation | 1,71 V ~ 1,89 V |

|

| Température de fonctionnement | -40°C ~ 105°C |

|

| Type de montage | Montage en surface, flanc mouillable |

|

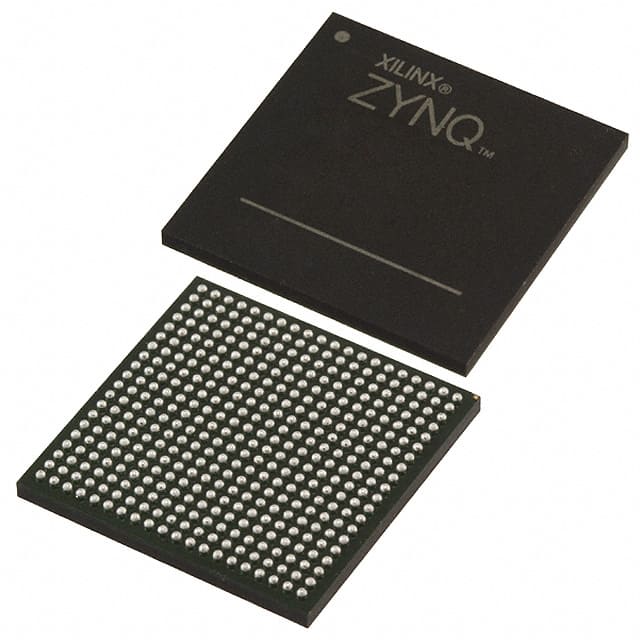

| Colis/Caisse | Tampon exposé 32-VFQFN |

|

| Package d'appareil du fournisseur | 32-VQFN (5x5) |

|

| Numéro de produit de base | DS90UB953 |

|

| SPQ | 3000 pièces |

UNSérialiseur/Désérialiseur(SerDes) est une paire de blocs fonctionnels couramment utilisés dans les communications à haut débit pour compenser les entrées/sorties limitées.Ces blocs convertissent les données entre les données série et les interfaces parallèles dans chaque direction.Le terme « SerDes » fait référence de manière générique aux interfaces utilisées dans diverses technologies et applications.L'utilisation principale d'un SerDes est d'assurer la transmission de données sur une seule ligne ou unpaire différentielleafin de minimiser le nombre de broches d'E/S et d'interconnexions.

La fonction de base de SerDes est composée de deux blocs fonctionnels : le bloc Parallel In Serial Out (PISO) (alias convertisseur parallèle-série) et le bloc Serial In Parallel Out (SIPO) (alias convertisseur série-parallèle).Il existe 4 architectures SerDes différentes : (1) SerDes à horloge parallèle, (2) SerDes à horloge intégrée, (3) SerDes 8b/10b, (4) SerDes à bits entrelacés.

Le bloc PISO (Parallel Input, Serial Output) possède généralement une entrée d'horloge parallèle, un ensemble de lignes d'entrée de données et des verrous de données d'entrée.Il peut utiliser un système interne ou externeboucle à verrouillage de phase (PLL)pour multiplier l'horloge parallèle entrante jusqu'à la fréquence série.La forme la plus simple du PISO comporte un seulregistre à décalagequi reçoit les données parallèles une fois par horloge parallèle et les décale à la fréquence d'horloge série la plus élevée.Les implémentations peuvent également utiliser undouble tamponinscrivez-vous pour évitermétastabilitélors du transfert de données entre domaines d'horloge.

Le bloc SIPO (Serial Input, Parallel Output) possède généralement une sortie d'horloge de réception, un ensemble de lignes de sortie de données et des verrous de données de sortie.L'horloge de réception peut avoir été récupérée à partir des données par le port série.récupération d'horlogetechnique.Cependant, les SerDes qui ne transmettent pas d'horloge utilisent une horloge de référence pour verrouiller la PLL sur la fréquence d'émission correcte, évitant ainsi les basses fréquences.fréquences harmoniquesprésent dans leflux de données.Le bloc SIPO divise ensuite l'horloge entrante jusqu'au débit parallèle.Les implémentations ont généralement deux registres connectés en tant que double tampon.Un registre est utilisé pour synchroniser le flux série et l'autre est utilisé pour conserver les données du côté parallèle le plus lent.

Certains types de SerDes incluent des blocs d’encodage/décodage.Le but de ce codage/décodage est généralement de placer au moins des limites statistiques sur le taux de transitions du signal afin de permettre une lecture plus facile.récupération d'horlogedans le récepteur, pour fournirencadrement, et de fournirSolde CC.

Caractéristiques du DS90UB953-Q1

- Qualifié AEC-Q100 pour les applications automobiles : conforme aux normes ISO 10605 et IEC 61000-4-2 ESD

- Température de l'appareil Grade 2 : température ambiante de fonctionnement de –40 °C à +105 °C

- Émetteur-récepteur compatible Power-over-Coax (PoC)

- Le sérialiseur de qualité 4,16 Gbit/s prend en charge les capteurs haute vitesse, notamment les imageurs Full HD 1080p 2,3 MP à 60 images/s et 4 MP à 30 images/s.

- Interface système compatible D-PHY v1.2 et CSI-2 v1.3 Synchronisation et synchronisation multi-caméras de précision

- Jusqu'à 4 voies de données à 832 Mbps par voie

- Prend en charge jusqu'à quatre canaux virtuels

- Générateur d'horloge de sortie programmable et flexible

- Protection des données et diagnostics avancés, y compris la protection des données CRC, la vérification de l'intégrité des données du capteur, la protection en écriture I2C, la mesure de la tension et de la température, l'alarme programmable et la détection des défauts de ligne.

- Prend en charge les câbles coaxiaux asymétriques ou à paires torsadées blindées (STP)

- Le canal de contrôle bidirectionnel I2C et GPIO à latence ultra faible permet le contrôle du FAI depuis l'ECU

- Alimentation unique de 1,8 V

- Faible consommation d'énergie (0,25 W typique)

- Compatible avec la sécurité fonctionnelleCompatible avec les désérialiseurs DS90UB954-Q1, DS90UB964-Q1, DS90UB962-Q1, DS90UB936-Q1, DS90UB960-Q1, DS90UB934-Q1 et DS90UB914A-Q1

- Documentation disponible pour faciliter la conception du système ISO 26262

- Large plage de température : –40°C à 105°C

- Petit boîtier VQFN de 5 mm × 5 mm et taille de solution PoC pour les conceptions de modules de caméra compacts

Description du DS90UB953-Q1

Le sérialiseur DS90UB953-Q1 fait partie de la famille de dispositifs FPD-Link III de TI conçus pour prendre en charge des capteurs de données brutes à haute vitesse, notamment des imageurs 2,3 MP à 60 ips, ainsi que des caméras 4 MP à 30 ips, un RADAR satellite, un LIDAR et un indicateur de temps. capteurs de vol (ToF).La puce offre un canal aller de 4,16 Gbit/s et un canal de contrôle bidirectionnel à latence ultra faible de 50 Mbit/s et prend en charge l'alimentation via un seul câble coaxial (PoC) ou STP.Le DS90UB953-Q1 dispose de fonctionnalités avancées de protection des données et de diagnostic pour prendre en charge l'ADAS et la conduite autonome.Associé à un désérialiseur compagnon, le DS90UB953-Q1 offre une synchronisation précise de l'horloge et des capteurs multi-caméras.

Le DS90UB953-Q1 est entièrement qualifié AEC-Q100 avec une large plage de températures de -40 °C à 105 °C. Le sérialiseur est livré dans un petit boîtier VQFN de 5 mm × 5 mm pour les applications de capteurs à espace limité.