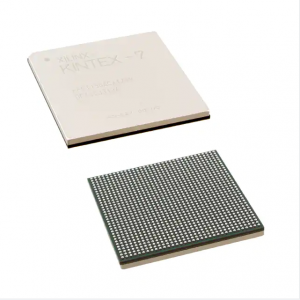

Xilinx/XC7K480T-2FFG1156I/XC7K480T/IC BOM FPGA/circuit intégré

Caractéristiques

| Attribut du produit | Valeur d'attribut |

| Fabricant: | Xilinx |

| Catégorie de produit: | FPGA – Réseau de portes programmable sur site |

| RoHS : | Détails |

| Série: | XC7K480T |

| Nombre d'éléments logiques : | 477760 LE |

| Nombre d'E/S : | 400 E/S |

| Tension d'alimentation - Min : | 1 V |

| Tension d'alimentation - Max : | 1 V |

| Température de fonctionnement minimale : | - 40 °C |

| Température de fonctionnement maximale : | + 100°C |

| Débit de données: | 12,5 Go/s |

| Nombre d'émetteurs-récepteurs : | 32 Émetteur-récepteur |

| Style de montage : | CMS/CMS |

| Colis/Caisse : | FCBGA-1156 |

| Marque: | Xilinx |

| RAM distribuée : | 6788 kbits |

| RAM de bloc intégrée – EBR : | 34380 kbits |

| Fréquence de fonctionnement maximale : | 640 MHz |

| Sensible à l'humidité : | Oui |

| Nombre de blocs de réseau logique – LAB : | 37325 LABORATOIRE |

| Tension d'alimentation de fonctionnement : | 1 V |

| Type de produit: | FPGA – Réseau de portes programmable sur site |

| Quantité par paquet d'usine : | 1 |

| Sous-catégorie : | CI logiques programmables |

| Nom commercial : | Kintex |

Présentation des FPGA XC7K480T-2FFG1156I

Description générale

Les FPGA Xilinx® série 7 comprennent quatre familles de FPGA qui répondent à la gamme complète des exigences du système, allant des applications à faible coût, petit facteur de forme, sensibles aux coûts et à grand volume jusqu'à la bande passante de connectivité ultra haut de gamme, la capacité logique et la capacité de traitement du signal. pour les applications hautes performances les plus exigeantes.Les FPGA de la série 7 comprennent :

• Famille Spartan®-7 : optimisée pour un faible coût, une consommation réduite et des performances d'E/S élevées.Disponible dans un boîtier à faible coût et de très petit facteur de forme pour une empreinte PCB minimale.

• Famille Artix®-7 : optimisée pour les applications à faible consommation nécessitant des émetteurs-récepteurs série et un débit DSP et logique élevé.Fournit le coût total de nomenclature le plus bas pour les applications à haut débit et sensibles aux coûts.

• Famille Kintex®-7 : optimisée pour le meilleur rapport qualité-prix avec une amélioration 2X par rapport à la génération précédente, permettant une nouvelle classe de FPGA.

• Famille Virtex®-7 : optimisée pour des performances et une capacité système les plus élevées avec une amélioration de 2 fois les performances du système.Appareils aux capacités les plus élevées grâce à la technologie d'interconnexion en silicium empilé (SSI).

Construits sur une technologie de processus de pointe, hautes performances, faible consommation (HPL), 28 nm et grille métallique à haute k (HKMG), les FPGA de la série 7 permettent une augmentation sans précédent des performances du système avec 2,9 To/ s de bande passante d'E/S, une capacité de 2 millions de cellules logiques et un DSP de 5,3 TMAC/s, tout en consommant 50 % d'énergie en moins que les appareils de la génération précédente pour offrir une alternative entièrement programmable aux ASSP et ASIC.

Caractéristiques

• Logique FPGA hautes performances avancée basée sur une véritable technologie de table de recherche (LUT) à 6 entrées configurable en tant que mémoire distribuée.

• Bloc RAM double port de 36 Ko avec logique FIFO intégrée pour la mise en mémoire tampon des données sur puce.

• Technologie SelectIO™ hautes performances avec prise en charge des interfaces DDR3 jusqu'à 1 866 Mb/s.

• Connectivité série haut débit avec émetteurs-récepteurs multi-gigabit intégrés de 600 Mb/s à des débits maximum de 6,6 Gb/s jusqu'à 28,05 Gb/s, offrant un mode spécial basse consommation, optimisé pour les interfaces puce à puce .

• Une interface analogique configurable par l'utilisateur (XADC), intégrant deux convertisseurs analogique-numérique 12 bits 1 MSPS avec des capteurs thermiques et d'alimentation sur puce.

• Tranches DSP avec multiplicateur 25 x 18, accumulateur 48 bits et pré-additionneur pour un filtrage haute performance, y compris un filtrage à coefficient symétrique optimisé.

• Puissantes tuiles de gestion d'horloge (CMT), combinant des blocs de boucle à verrouillage de phase (PLL) et de gestionnaire d'horloge en mode mixte (MMCM) pour une haute précision et une faible gigue.

• Bloc intégré pour PCI Express® (PCIe), pour des conceptions de points de terminaison et de ports racine jusqu'à x8 Gen3.

• Grande variété d'options de configuration, notamment la prise en charge des mémoires de base, le cryptage AES 256 bits avec authentification HMAC/SHA-256, ainsi que la détection et la correction SEU intégrées.

• Boîtier à puce retournée à faible coût, filaire, sans couvercle et à haute intégrité du signal, offrant une migration facile entre les membres de la famille dans le même boîtier.Tous les forfaits disponibles en forfaits sans Pb et certains forfaits en option Pb.

• Conçu pour des performances élevées et une consommation minimale avec 28 nm, HKMG, processus HPL, technologie de traitement de tension de cœur de 1,0 V et option de tension de cœur de 0,9 V pour une puissance encore plus faible.

La série Xilinx FPGA (Field Programmable Gate Array) XC7K480T-2FFG1156I est FPGA, Kintex-7, MMCM, PLL, 400 E/S, 710 MHz, 477760 cellules, 970 mV à 1,03 V, FCBGA-1156, voir les substituts et les alternatives avec les fiches techniques, les stocks, les prix des distributeurs agréés sur FPGAkey.com, et vous pouvez également rechercher d'autres produits FPGA.

Caractéristiques

Logique FPGA avancée hautes performances basée sur une véritable technologie de table de recherche (LUT) à 6 entrées configurable en tant que mémoire distribuée.

Bloc de RAM double port de 36 Ko avec logique FIFO intégrée pour la mise en mémoire tampon des données sur puce.

Technologie SelectIO hautes performances avec prise en charge des interfaces DDR3 jusqu'à 1 866 Mb/s.

Connectivité série haut débit avec émetteurs-récepteurs multi-gigabit intégrés de 600 Mb/s à des débits maximum de 6,6 Gb/s jusqu'à 28,05 Gb/s, offrant un mode spécial basse consommation, optimisé pour les interfaces puce à puce.

Une interface analogique configurable par l'utilisateur (XADC), intégrant deux convertisseurs analogique-numérique 12 bits 1 MSPS avec des capteurs thermiques et d'alimentation sur puce.

Tranches DSP avec multiplicateur 25 x 18, accumulateur 48 bits et pré-additionneur pour un filtrage haute performance, y compris un filtrage à coefficient symétrique optimisé.

De puissantes tuiles de gestion d'horloge (CMT), combinant des blocs de boucle à verrouillage de phase (PLL) et de gestionnaire d'horloge en mode mixte (MMCM) pour une haute précision et une faible gigue.

Bloc intégré pour PCI Express (PCIe), pour des conceptions de points de terminaison et de ports racine jusqu'à x8 Gen3.

Grande variété d'options de configuration, notamment la prise en charge des mémoires de base, le cryptage AES 256 bits avec authentification HMAC/SHA-256, ainsi que la détection et la correction SEU intégrées.

Emballage à puce retournée à faible coût, filaire, sans couvercle et à haute intégrité du signal, offrant une migration facile entre les membres de la famille dans le même emballage.Tous les forfaits disponibles en forfaits sans Pb et certains forfaits en option Pb.

Conçu pour des performances élevées et une consommation minimale avec 28 nm, HKMG, processus HPL, technologie de processus de tension de cœur de 1,0 V et option de tension de cœur de 0,9 V pour une puissance encore plus faible.