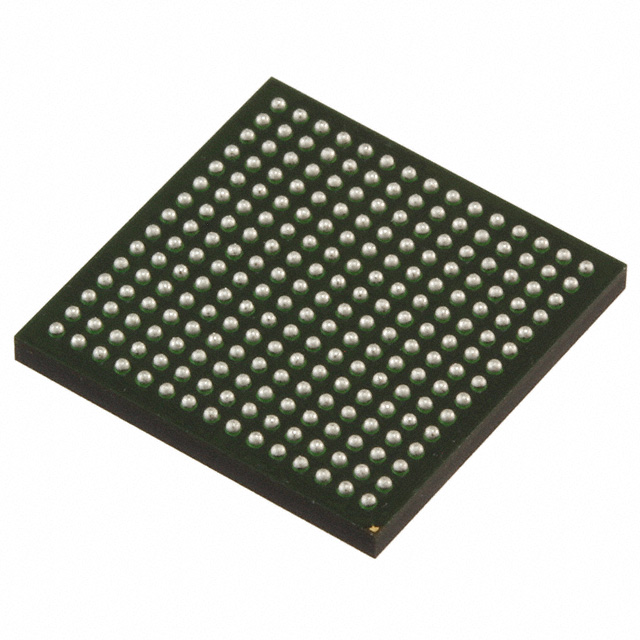

Circuit intégré XC5VLX85T-1FFG1136C nouveau et Original

Attributs du produit

| TAPER | DESCRIPTION | SÉLECTIONNER |

| Catégorie | Circuits intégrés (CI) |

|

| Fabricant | AMD Xilinx |

|

| Série | Virtex®-5 LXT |

|

| Emballer | Plateau |

|

| État du produit | Actif |

|

| Nombre de LAB/CLB | 6480 |

|

| Nombre d'éléments logiques/cellules | 82944 |

|

| Nombre total de bits de RAM | 3981312 |

|

| Nombre d'E/S | 480 |

|

| Tension – Alimentation | 0,95 V ~ 1,05 V |

|

| Type de montage | Montage en surface |

|

| Température de fonctionnement | 0°C ~ 85°C (JT) |

|

| Colis/Caisse | 1136-BBGA, FCBGA |

|

| Package d'appareil du fournisseur | 1136-FCBGA (35×35) |

|

| Numéro de produit de base | XC5VLX85 |

|

Signaler une erreur d'informations sur le produit

Voir similaire

Documents et médias

| TYPE DE RESSOURCE | LIEN |

| Feuilles de données | Présentation de la famille Virtex-5 |

| Informations environnementales | Certifié RoHS de Xiliinx |

| Conception/Spécification PCN | Avis sans plomb pour les navires croisés 31/octobre/2016 |

Classifications environnementales et d'exportation

| ATTRIBUT | DESCRIPTION |

| Statut RoHS | Conforme ROHS3 |

| Niveau de sensibilité à l'humidité (MSL) | 4 (72 heures) |

| Statut REACH | REACH non affecté |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

Réseau de portes programmables sur site

UNréseau de portes programmable sur site(FPGA) est uncircuit intégréconçu pour être configuré par un client ou un concepteur après fabrication – d'où le termeprogrammable sur site.La configuration FPGA est généralement spécifiée à l'aide d'unlangage de description du matériel(HDL), similaire à celui utilisé pour uncircuit intégré spécifique à une application(ASIC).Schémas de circuitsétaient auparavant utilisés pour spécifier la configuration, mais cela est de plus en plus rare en raison de l'avènement deautomatisation de la conception électroniqueoutils.

Les FPGA contiennent un ensemble deprogrammable blocs logiques, et une hiérarchie d'interconnexions reconfigurables permettant de relier les blocs entre eux.Les blocs logiques peuvent être configurés pour effectuer desfonctions combinatoires, ou agissez simplementdes portes logiquescommeETetXOR.Dans la plupart des FPGA, les blocs logiques incluent égalementéléments de mémoire, ce qui peut être simpletongsou des blocs de mémoire plus complets.[1]De nombreux FPGA peuvent être reprogrammés pour mettre en œuvre différentsfonctions logiques, permettant une flexibilitéinformatique reconfigurabletel qu'il est exécuté danslogiciel.

Les FPGA jouent un rôle remarquable danssystème embarquédéveloppement en raison de leur capacité à démarrer le développement de logiciels système simultanément avec le matériel, à permettre des simulations de performances du système à un stade très précoce du développement et à permettre divers essais de système et itérations de conception avant de finaliser l'architecture du système.[2]

Histoire[modifier]

L'industrie des FPGA est née demémoire morte programmable(PROM) etdispositifs logiques programmables(PLD).Les PROM et les PLD avaient tous deux la possibilité d'être programmés par lots en usine ou sur le terrain (programmables sur site).[3]

Altèrea été fondée en 1983 et a livré le premier dispositif logique reprogrammable de l'industrie en 1984 – l'EP300 – qui comportait une fenêtre en quartz dans l'emballage permettant aux utilisateurs d'allumer une lampe ultraviolette sur la puce pour effacer leEPROMcellules contenant la configuration du périphérique.[4]

Xilinxproduit le premier ordinateur programmable sur le terrain commercialement viableréseau de portesen 1985[3]– le XC2064.[5]Le XC2064 était doté de portes programmables et d'interconnexions programmables entre les portes, les prémices d'une nouvelle technologie et d'un nouveau marché.[6]Le XC2064 disposait de 64 blocs logiques configurables (CLB), avec deux trois entréesTables de recherche(LUT).[7]

En 1987, leCentre de guerre de surface navalea financé une expérience proposée par Steve Casselman pour développer un ordinateur capable de mettre en œuvre 600 000 portes reprogrammables.Casselman a réussi et un brevet lié au système a été délivré en 1992.[3]

Altera et Xilinx sont restées incontestées et ont connu une croissance rapide de 1985 au milieu des années 1990, lorsque des concurrents ont surgi, érodant une partie importante de leur part de marché.En 1993, Actel (aujourd'huiMicrosemi) desservait environ 18 pour cent du marché.[6]

Les années 1990 ont été une période de croissance rapide pour les FPGA, tant en termes de sophistication des circuits que de volume de production.Au début des années 1990, les FPGA étaient principalement utilisés danstélécommunicationsetla mise en réseau.À la fin de la décennie, les FPGA ont trouvé leur place dans les applications grand public, automobiles et industrielles.[8]

En 2013, Altera (31 %), Actel (10 %) et Xilinx (36 %) représentaient ensemble environ 77 % du marché des FPGA.[9]

Des entreprises comme Microsoft ont commencé à utiliser les FPGA pour accélérer les systèmes hautes performances et gourmands en calcul (comme lecentres de donnéesqui exploitent leurMoteur de recherche Bing), en raison deperformance par wattavantage qu'offrent les FPGA.[dix]Microsoft a commencé à utiliser les FPGA pouraccélérerBing en 2014 et en 2018 ont commencé à déployer des FPGA sur d'autres charges de travail de centres de données pour leurAzur Cloud computingplate-forme.[11]

Les délais suivants indiquent les progrès réalisés dans différents aspects de la conception des FPGA :

portes

- 1987 : 9 000 portes, Xilinx[6]

- 1992 : 600 000, Département de la guerre navale de surface[3]

- Début des années 2000 : millions[8]

- 2013 : 50 millions, Xilinx[12]

La taille du marché

- 1985 : Premier FPGA commercial : Xilinx XC2064[5][6]

- 1987 : 14 millions de dollars[6]

- c.1993 : >385 millions de dollars[6][échec de la vérification]

- 2005 : 1,9 milliard de dollars[13]

- Estimations 2010 : 2,75 milliards de dollars[13]

- 2013 : 5,4 milliards de dollars[14]

- Estimation 2020 : 9,8 milliards de dollars[14]

La conception commence

UNdébut de la conceptionest une nouvelle conception personnalisée pour une implémentation sur un FPGA.

Conception[modifier]

Les FPGA contemporains disposent de grandes ressources dedes portes logiqueset des blocs RAM pour mettre en œuvre des calculs numériques complexes.Comme les conceptions FPGA utilisent des débits d'E/S très rapides et des données bidirectionnellesles autobus, il devient difficile de vérifier le timing correct des données valides dans le temps de configuration et le temps de maintien.

Planification de l'étagepermet l’allocation des ressources au sein des FPGA pour répondre à ces contraintes de temps.Les FPGA peuvent être utilisés pour implémenter n'importe quelle fonction logique qu'unASICpeut effectuer.La possibilité de mettre à jour la fonctionnalité après l'expédition,reconfiguration partielled'une partie du dessin[17]et les faibles coûts d'ingénierie non récurrents par rapport à une conception ASIC (malgré le coût unitaire généralement plus élevé) offrent des avantages pour de nombreuses applications.[1]

Certains FPGA possèdent des fonctionnalités analogiques en plus des fonctions numériques.La fonctionnalité analogique la plus courante est unvitesse de balayagesur chaque broche de sortie, permettant à l'ingénieur de définir des taux bas sur des broches légèrement chargées qui autrementanneauoucoupleinacceptable, et de fixer des débits plus élevés sur les broches fortement chargées sur les canaux à grande vitesse qui, autrement, fonctionneraient trop lentement.[18][19]Le quartz est également courant.oscillateurs à cristal, oscillateurs résistance-capacité sur puce, etboucles à verrouillage de phaseavec intégréoscillateurs commandés en tensionutilisé pour la génération et la gestion d'horloge ainsi que pour les horloges de transmission du sérialiseur-désérialiseur à grande vitesse (SERDES) et la récupération de l'horloge du récepteur.Les différentiels sont assez courantscomparateurssur les broches d'entrée conçues pour être connectées àsignalisation différentiellecanaux.Quelques "signal mixteLes FPGA »ont des périphériques intégrésconvertisseurs analogique-numérique(ADC) etconvertisseurs numérique-analogique(DAC) avec des blocs de conditionnement de signaux analogiques leur permettant de fonctionner comme unsystème sur puce(SoC).[20]De tels dispositifs brouillent la frontière entre un FPGA, qui transporte des uns et des zéros numériques sur sa structure d'interconnexion programmable interne, etréseau analogique programmable sur site(FPAA), qui transporte des valeurs analogiques sur sa structure d'interconnexion programmable interne.